C2H

贡献者:dolphin 浏览:1527次 创建时间:2014-06-11

-

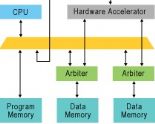

C2H 是一种可以直接对ANSI C 函数定制硬件加速的技术,在推出短短的一年时间内就得到了嵌入式及FPGA 设计者的广泛使用。C2H 编译器能分析程序要加速实现的存储器接口类型,生成硬件加速器逻辑以及合适的AvalON(总线互联架构)的主机和从机接口,达到与存储器延时的匹配。这样,分担了处理器的数据计算和存储器访问任务,使处理器能够更好的处理其他任务。

C2H 是一种可以直接对ANSI C 函数定制硬件加速的技术,在推出短短的一年时间内就得到了嵌入式及FPGA 设计者的广泛使用。C2H 编译器能分析程序要加速实现的存储器接口类型,生成硬件加速器逻辑以及合适的AvalON(总线互联架构)的主机和从机接口,达到与存储器延时的匹配。这样,分担了处理器的数据计算和存储器访问任务,使处理器能够更好的处理其他任务。C2H的使用需要进行反复的调试,直到性能符合设计要求。具体流程如下:

(1)在NiosII中开发和调试C程序;

(2)分析C程序,找到最适合加速的部分;

(3)将需要加速的代码段写成一个独立的子函数;

(4)指定这个函数为硬件加速的函数;

(5)在NiosII IDE中重新编译整个工程;

(6)分析硬件加速的结果,观察C2H报告;

开放分类

参考资料

贡献者

本词条在以下词条中被提及:

关于本词条的评论共:(0条)

RSS订阅

RSS订阅