FIR数字滤波器

贡献者:dolphin 浏览:1077次 创建时间:2014-06-11

-

FIR数字滤波器的对称特性,可以先进行加法运算,然后对加法运算的结果进行串行乘累加运算,从而得到改进的串行结构。与串行结构相比,改进的滤波器完成一次滤波的时钟周期减半,乘累加次数减半,提高了处理速度,但同时要消耗更多的硬件资源。

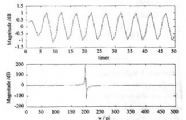

FIR数字滤波器的对称特性,可以先进行加法运算,然后对加法运算的结果进行串行乘累加运算,从而得到改进的串行结构。与串行结构相比,改进的滤波器完成一次滤波的时钟周期减半,乘累加次数减半,提高了处理速度,但同时要消耗更多的硬件资源。从串行结构中可以看出,FIR滤波过程就是一个信号逐级延迟的过程,将各级延迟输出加权累加,得到滤波输出,其中最主要的运算是乘累加运算。FIR每完成一次滤波过程需要进行N次乘法和(N-1)次加法运算,N为滤波器的阶数。所以,滤波器的运算量完全取决于N的大小,当N很大时,延迟将非常长,无法实现高速信号处理。

将串行结构展开,根据滤波器的信号流图用多个乘法器和加法器并行实现,得到FIR滤波器的并行实现结构,如图1(c)所示。并行滤波器的滤波速度快,一个时钟周期内完成一次滤波,但消耗大量的FPGA资源,如乘累加器,且器件的延迟较大,工作频率不宜太高。

开放分类

参考资料

贡献者

本词条在以下词条中被提及:

关于本词条的评论共:(0条)

RSS订阅

RSS订阅